Hirdetés

- gban: Ingyen kellene, de tegnapra

- Lalikiraly: Astra kalandok @ Negyedik rész

- Brogyi: CTEK akkumulátor töltő és másolatai

- ubyegon2: Airfryer XL XXL forrólevegős sütő gyakorlati tanácsok, ötletek, receptek

- NASsoljunk: ZyXEL NSA-310 és az FFP

- Luck Dragon: Asszociációs játék. :)

- sziku69: Szólánc.

- jakra: Retro gyujtemenyem (cloud synced for safety...)

- sziku69: Fűzzük össze a szavakat :)

- GoodSpeed: Norton 360 Premium: 75GB Cloud PC Backup for 10 Devices 14.99€-ért? Igen!

Új hozzászólás Aktív témák

-

S_x96x_S

addikt

>> "és frekvencia regresszió ott már túl nagy lett volna"

> Szvsz ennyire nem fogyaszt sokat egy gyorsítótár.jó kérdés ..

az én megértésem (~spekulációm) szerint -

ez alapján:

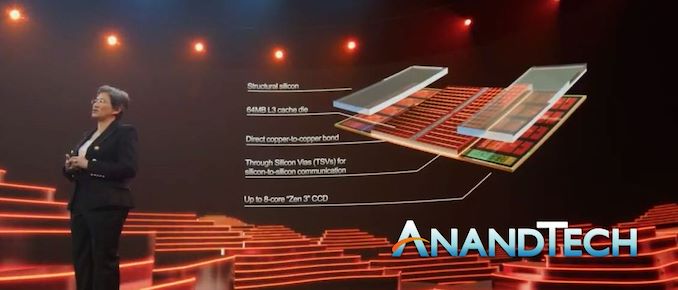

https://www.anandtech.com/show/16725/amd-demonstrates-stacked-vcache-technology-2-tbsec-for-15-gaming ( May 31, 2021 )valamennyivel biztosan többet fogyaszt,

-mivel a technológiából eredően egymásra vannak pakolva ..

és így a hőtermelés elvezetése nem olyan egyszerű.

-És még ha le is van kapcsolva[1] .. fizikiailag az is akadályozza (~rontja) a hő elvezetését - az alsó rétegből[2]

-nem egy sikban van az extra cache .. hanem valami felett [3]

és ugyanakkora alapterületen több hő keletkezik.

- És a nagyobb (>200x ) interconnect density [4] - hőelvezetési problémához vezet.

- és ez még csak 2 réteg. [5][1] "The V-Cache is address striped with the normal L3 and can be powered down when not in use. The V-Cache sits on the same power plane as the regular L3."

[2] "The other element is thermals – usually you want the logic on the top die to manage the thermals better as it is close to the heatspreader/heatsink, but moving logic further away from the substrate means that power has to be transported up to the top die. Intel is hoping to mix microbumps and TSVs in upcoming technologies, and TSMC has a similar roadmap for the future for its customers."

[3]

[4] "this packaging enables a >200x interconnect density"[5] "Starting with the technology, this is clearly TSMC’s SoIC Chip-on-Wafer in action, albeit with only two layers. TSMC has demonstrated twelve layers, however those were non-active layers.

The problem with stacking silicon is going to be in the activity,

and subsequently thermals .

We’ve seen with other TSV stacked hardware, like HBM, that SRAM/memory/cache is the perfect vehicle for this as it doesn’t add that much to the thermal requirements of the processor. The downside is that the cache you stack on top is little more than just cache." -

Ueda

senior tag

Szvsz ennyire nem fogyaszt sokat egy gyorsítótár.

Nem tudom ... nekem ilyen tapasztlatom van :

Engemet meglepett (helyesebben mondva zavart) a megnövekedett hőtermelés és fogyasztás, amikor Q8200 -ről Q9650 -re váltottam. Azt gondoltam, hogy a kisebb teljesítményű modellek eleve a rosszabb csipekből kerülnek ki. Ehhez képest a Q8200 jégcsap volt a Q9650 -hez képest. 4 MB vs 12 MB L2 cache. Szerintem az optimális a 8 MB L2 volt, ami a Q6600 -ban volt.

Új hozzászólás Aktív témák

- Gyúrósok ide!

- AMD GPU-k jövője - amit tudni vélünk

- Milyen légkondit a lakásba?

- Battlefield 6

- Konkrét moderációval kapcsolatos kérdések

- „Ezt a sorozatot emberek készítették!”

- Becsszó, még mindig készül a Half-Life 3!

- Futás, futópályák

- Építő/felújító topik

- Okos Otthon / Smart Home

- További aktív témák...

- Xiaomi Redmi Note 14 Pro 5G 8/256GB, Újszerű, Kártyafüggetlen, Töltővel, Dobozzal, 1 Év Garanciával!

- ROG Strix G731GW 17.3" FHD IPS i7-9750H RTX 2070 16GB 1TB NVMe magyar vbill gar

- Samsung Galaxy A26 5G 6/128GB, Megkímélt, Kártyafüggetlen, Töltővel, 1 Év Garanciával!

- Dali Concept 1

- X1 Nano Gen1 13" 2K IPS i7-1160G7 16GB 1TB NVMe ujjlolv IR kam gar

- LÉZEREZÉS! külföldi billentyűzet magyarra kb. 20-30p alatt!

- UPDATE!!! Lenovo ThinkPad // T - Széria // X1 carbon // X1 Yoga 2-in-1 // és a többiek... 5-11 gen.

- HATALMAS AKCIÓK! GARANCIA, SZÁMLA - Windows 10 11, Office 2016 2019 2021,2024, vírusírtók, VPN

- DELL PowerEdge R730xd 16LFF 160TB+400GB 2U rack - 2xE5-2683v4 (16c/32t),256GB RAM,2x10G NET,HBA330

- AKCIÓ! Apple Studio Display 27 5K Nanotexturált üveg monitor garanciával hibátlan működéssel

Állásajánlatok

Cég: PCMENTOR SZERVIZ KFT.

Város: Budapest

Cég: Laptopműhely Bt.

Város: Budapest