Hirdetés

- ubyegon2: Airfryer XL XXL forrólevegős sütő gyakorlati tanácsok, ötletek, receptek

- Gurulunk, WAZE?!

- sziku69: Fűzzük össze a szavakat :)

- Luck Dragon: Asszociációs játék. :)

- eBay-es kütyük kis pénzért

- petipetya: Nagy chili topic. :)

- sziku69: Szólánc.

- GoodSpeed: Ebes, a megtervezett falu!

- D1Rect: Nagy "hülyétkapokazapróktól" topik

- NASsoljunk: ZyXEL NSA-310 és az FFP

Új hozzászólás Aktív témák

-

Petykemano

veterán

válasz

Petykemano

#1905

üzenetére

Petykemano

#1905

üzenetére

Charlie 15 lapkás infója

Kitart mellette.

Azon gondolkodtam, hogy vajon nem lehet-e ehhez hasonló megoldás:

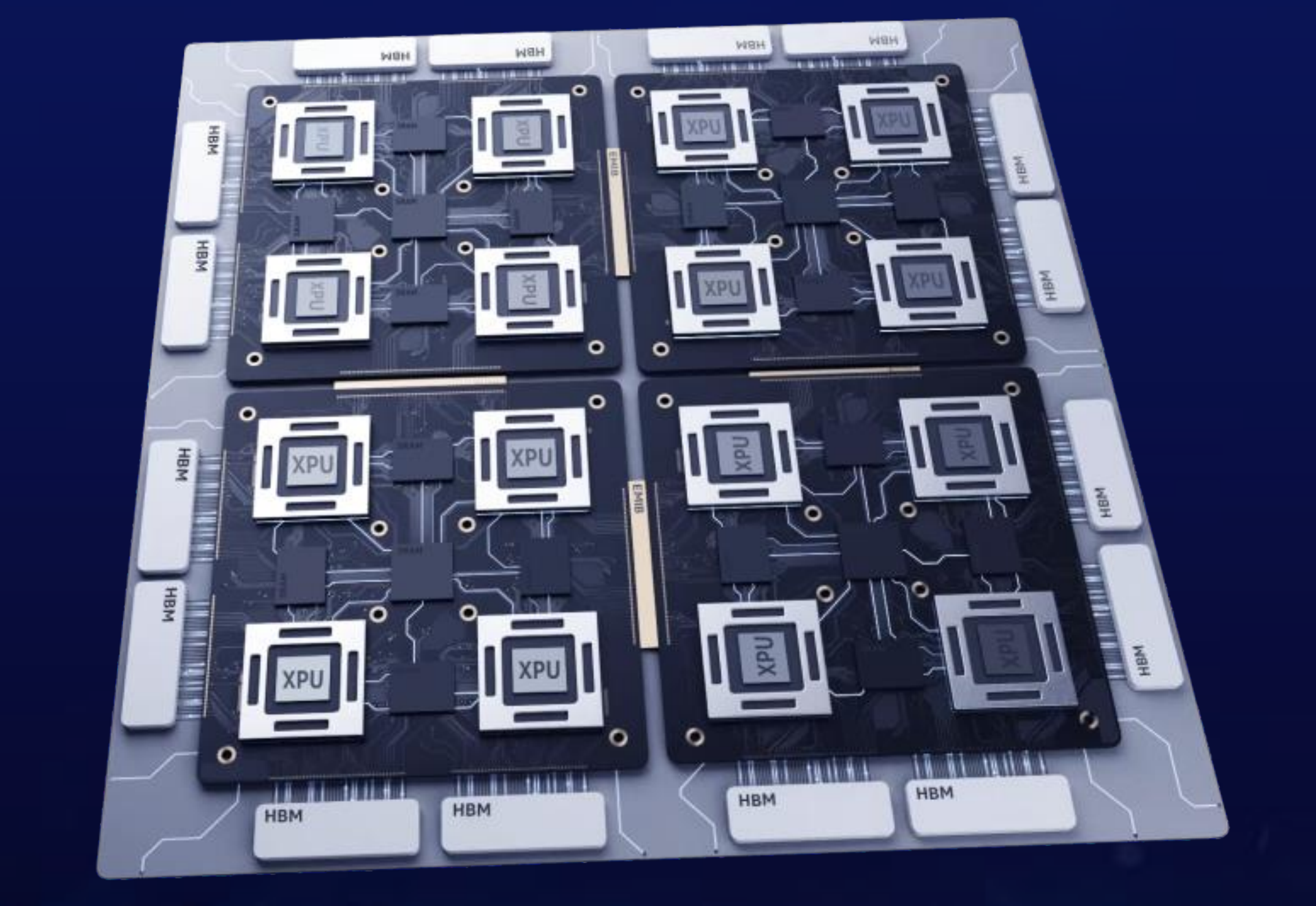

Ez egy ilyen kép, ahol az ún XPU-k közötti fekete chipek elvileg adatmegosztást célzó SRAM-ok.

Eddig ugye mindig abban gondolkodtunk, hogy az IO lapkában van-e L4 cache.

De abban is gondolkodtunk, hogy vajon legalább az egymáshoz közeli chipletek között van-e direkt IF link. Ezt végül cáfolták. (Ez persze nem jelenti azt, hogy az ötlet fel se merülhetne)Azt ugye tudjuk, hogy a zen3-mal CCX=CCD.

Mondjuk tényleg mi van, ha a 6 plusz lapkából (according to Charlie) 2 tényleg valami IO-lapkához kötődő valami (HBM?), ami L4 cache-ként funkcionál közvetlenül a memória irányába. 4 pedig az egymás mellett levő chipletek közé kerül (úgy mint a fenti képen, csak ott nem két egymás melletti CCD van, hanem 1XPU)

Akkor 1 ilyen kommunikációs lapka pont össze tudna kötni egymással 4 CCD-t.(Hogy milyen haszna lenne, azt nem tudom megmondani, de ha nem lehetne haszna, az intel ne mutogatna ilyen képeket.)

-

S_x96x_S

addikt

válasz

Petykemano

#1905

üzenetére

Petykemano

#1905

üzenetére

> Zen3: smt4 ...

én elképzelhetőnek tartom, hogy valóban megcélozták az smt4-et.

de volt mellette 2 másik - kisebb változtatást igénylő design.

És amikor a legyártott mintapéldányokat tesztelték, az eredmények alapján pillanatnyilag - dobták az smt4-es verziót.A csúszások alapján látszik

,hogy azért van sok technikai probléma amit meg kell oldani

,viszont a piac elvárja, hogy valami újdonságot jövőre is szállítsanak.

tehát valami biztonsági terv is kell.

Az is lehet, hogy most a biztonsági verziót hallottuk.

szerintem az smt4 sincs teljesen kizárva ( csak le csökkent a valószínűsége )

Új hozzászólás Aktív témák

- BestBuy topik

- Őrületes specifikációkkal rendelkezik a Tachyum csodaprocesszora

- Billiós befektetéssel bővül a Samsung magyarországi akkugyára

- alza vélemények - tapasztalatok

- rx 9070 xt

- Milyen NAS-t vegyek?

- Konzolokról KULTURÁLT módon

- Kertészet, mezőgazdaság topik

- Milyen routert?

- Viccrovat

- További aktív témák...

- LG UltraFine 4K és Smart Monitorok: BLACK NOVEMBER -30%

- BESZÁMÍTÁS! MSI Z270 GAMING PRO CARBON alaplap garanciával hibátlan működéssel

- Samsung Galaxy S23 / 8/128GB / Kártyafüggetlen / 12Hó Garancia

- HIBÁTLAN iPhone 13 Pro Max 256GB Sierra Blue -1 ÉV GARANCIA - Kártyafüggetlen, MS3958, 100% Akksi

- BESZÁMÍTÁS! Sony PlayStation 5 Slim 1TB SSD Lemezes konzol Elite kontrollerrel garanciával hibátlan

Állásajánlatok

Cég: PCMENTOR SZERVIZ KFT.

Város: Budapest

Cég: Laptopműhely Bt.

Város: Budapest