Vissza a jövőbe

A Neumann János díjas amerikai Ivan Edward Sutherland egyik, Wheel of Reincarnation (~az újjászületés kereke) elnevezésű 1968-as szabályának lényegi jelentése szerint, olcsóbb kiváltani egy speciális célú hardvert (pl.: GPU) a megfelelő szoftver és egy általános célra készített hardver (pl.: CPU) kombinációjával. Viszont olykor a piacnak nagyobb szüksége van a magasabb számítási teljesítményre mint az olcsóbb hardverekre, így idővel ennek érdekében a funkció kikerül az általános célra készített hardverből, és egy külső speciális célú egység formájában születik újjá. Később ha már a korábbi, még speciális célú hardver feladatai már túl általánossá válnak, akkor a költségek csökkentése érdekében visszakerül az általános célra készített hardverbe, mellyel kialakul egy ördögi kör.

Vissza a jövőbe

...egészen 1989 végéig amikor Szűrös Mátyás kikiáltja a Magyar Köztársaságot és az Intel forgalomba hozza az i486DX nevű CPU szériáját. Ennek a központi egységnek az egyik nagy újítása volt, hogy az elsőként tartalmazta a CPU-val egy közös szilíciumlapkába integrálva a matematikai koprocesszort, azaz az FPU-t (Floating-Point Unit, pontosabb fordításban lebegőpontos egység). Ez az egység a lebegőpontos matematikai műveleteket jelentős meggyorsítására lett hivatott. Ezt megelőzően az FPU nem volt szerves része a CPU-nak, csak külön extraként volt megvásárolható és az alaplapon található direkt erre szánt foglalatba volt illeszthető. Ekkoriban még leginkább csak különböző speciális mérnöki tervező szoftverek igényelték a plusz egységet. Az AutoCAD 1987 szeptemberében megjelent Release 9-es verziója például már nem volt hajlandó FPU nélkül elindulni.

Itt még külön. 386 és 387DX, balra a CPU jobbra az FPU.

Egy átlagfelhasználó ezzel szemben akár a 90es évek közepéig is vígan megvolt FPU nélkül. A legtöbb akkoriban népszerűnek számított alkalmazás és operációs rendszer ezen koprocesszor nélkül is élvezhetően futott. Példának okáért az egyik(?) első játék amely már nem volt hajlandó a lebegőpontos egység jelenléte nélkül elindulni az a 94' végén megjelent Heretic volt. A kritérium ellenére még ez sem pofitált komolyabban ebből, majd csak a másfél évvel később érkező Quake számított az első olyan 3D-s játéknak amely már jelentősen kihasználta az FPU nyújtotta előnyöket.

Az i486DX óta (a butított 486-os, pl. SX szériákat leszámítva) az összes forgalomba került x86-os CPU magonként rendelkezik a teljes, lebegőpontos utasításkészlet futtatásáért felelős egységgel/egységekkel.

Level UP

Az i486DX egy másik nagyobb újítása volt a lapkába integrált (ún. on-die) cache. Mindaddig ugyanis kizárólag az alaplapon található SRAM IC-k formájában létezhetett (külső - external) cache. Az i486DX 8 KB belső (internal) L1 cache-vel gazdagodott, de ezzel párhuzamosan megmaradt az alaplapon található cache is, amely így egy szintet feljebb (illetve pontosabban inkább lejjebb) csúszott amivel L2 cache vált belőle. Ennek a mérete ekkoriban még általában 256 KB körül mozgott. Értelemszerűen a külső magasabb szintű L2 cache jóval lassabb volt mint a lapkában elhelyezkedő L1. Ennek egyik oka az volt, hogy míg a belső L1 magórajelen addig a külső L2 csak az FSB órajelén üzemelt. Az L1 cache betelepülése is maradandó lett, mivel az FPU-hoz hasonlóan az ezután megjelent (i486DX-nél jobb) processzorok már hasonló módon tartalmazták ezt a gyorsítótárat.

Az i486-os lapka. Fent a nagyobb homogén terület a 8 KB cache.

Összességében elmondható, hogy az i486 a magas szintű integráció miatt egy mérföldkőnek számított a processzorok történelmében. Cache szempontjából a következő nagy állomás az 1995 novemberében megjelent és elsősorban szerverekbe szánt Pentium Pro lett. Itt már az L2 cache költözött be a CPU tokozásába amivel létrejött egy úgynevezett multi-chip module (MCM). Hasonló felépítésű a Core 2 Quad vagy a Core i3 és i5 (Clarkdale/Arrandale) is melyek szintén több (egészen pontosan kettő) lapkát foglalnak magukba egy tokozáson belül.

Pentium Pro 1 MB L2 cache-vel. A két színesebb, hasonló felépítésű egység egy-egy 512 KB méretű SRAM lapkát rejt.

A fenti képen jól kivehető, hogy az i486-tal ellentétben a cache(-ek) itt "csak" a CPU lapka mellé (off-die) és nem a CPU lapkába került(ek) be. Ennek ellenére az így létrejött L2 cache már a CPU magórajelén (full-speed) üzemelt amely jó hatással volt a számítási teljesítményre.

Az első immáron a CPU lapkába integrált (on-die) L2 cache eljövetelére még majd három évet kellett várni. Kissé talán meglepő módon ezt nem egy csúcsprocesszor, hanem az inkább tömegeknek, átlagfelhasználóknak szánt Celeron-A (Mendocino) hozta el 1998 augusztusában. Gyakorlatilag ez utóbbi és az azt megelőző sima Celeron (Covington) között csak a hozzáadott 128 KB L2 cache volt a különbség. A plusz gyorsítótártól a lapka mérete 131 mm²-ről 154 mm²-re nőtt. Ez a váltózás szabad szemmel is könnyen megfigyelhető: fent a Covington, lent a Mendocino. A szóban forgó 128 KB cache szintén magórajelen ketyegett. A Pentium Pro-hoz hasonlóan a Celeron-A sem hozta magával minden kategóriában a lapkába vagy mellé ültetett L2 cache-t. A Celeron-A után fél évvel megjelent Pentium II utódja a Pentium III (Katmai) ami még az elődhöz és a Pentium Pro-hoz hasonlóan off-die (vagy in-package) megoldást alkalmazott. Az L2 cache CPU lapka mellett a tokozáson került elhelyezésre, és csak a mindenkori magórajel pontosan felén üzemelt.

Az első PIII. Jobb oldalon látható az 512 KB "half-speed" L2 cache 2x256 KB-os elrendezésben.

Végül az Intel kínálatában a 99' októberében megjelent Coppermine kódnevű lapka hozta el minden szintre a lapkába integrált (on-die) L2 cache-t. Erre a lapkára meglehetősen sok Pentium III, Celeron modell épült az idők folyamán.

Most hirtelen 99' októberéből ugorjunk vissza pár hónapot a DeLorean-nal egészen négy nappal korábbra mint ahogy a fenti képen is látható első Pentium III megjelent, és szinte napra pontosan fél évvel későbbre a már megismert Celeron-A debütálásától. A pontos dátum 1999 február 22. mely napon az AMD útjára indította a K6-III sorozatot. Az első ilyen CPU a Sharptooth kódnevű lapkára épült és a Mendocino által tartalmazott L2 mennyiség pontosan dupláját tartalmazta azaz 256 KB-ot ami szintén magórajelen működött.

Sharptooth lapka. Jobb szélen az L2 cache.

Az Intel-hez hasonlóan legelső lapkába integrált L2 megoldásukkal az AMD sem dobta sutba az off-die L2 cache ötletét. A négy hónappal később érkező első K7 alapú Athlon a Katmai-hoz hasonló elgondolással tartalmazta a másodszintű gyorsítótárat.

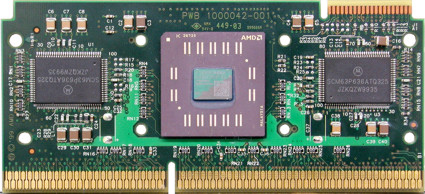

Az első Athlon széria tagja, Slot A tokozással.

Végül a 2000 júniusában érkezett Thunderbird lapkával gyakorlatilag mindkét gyártónál minden kategóriában alapértelmezetté vált az on-die L2 cache. Ettől kezdve egészen a 2006 januárjában megjelent mobil Core Duo-ig (Yonah) bezárólag még az a megállapítás is helytálló volt, hogy minden újonnan debütált CPU mag saját dedikált L2 cache-vel rendelkezik. A Yonah ezt annyiban rúgta fel, hogy ennél két mag osztozott egyetlen nagyobbnak mondható 2MB-os L2 cache-en. A Core 2 Duo ezt vitte tovább ahol először 4 (Conroe), majd később 6 MB (Penryn) másodszintű gyorsítótáron osztozhatott a két mag.

A Conroe sematikus felépítése.

A Core 2 sorozat megosztott másodszintű gyorsítótárának okáról következzen itt egy rövid magyarázat fLeSs tollából, melyet jó ha fejben tartunk a továbbiakhoz:

"Az Advanced Smart Cache (továbbfejlesztett intelligens gyorsítótár) nem más, mint a Core processzorokban található megosztott, továbbfejlesztett gyorsítótár "beceneve". Intelligens (smart) elnevezését annak köszönheti, hogy a Core-ban a másodlagos gyorsítótáron a két processzormag megosztozik. Az Intel úgy fejlesztette ki az L2 cache-t, hogy ahhoz a két mag bármikor hozzáférjen, tehát a Core esetében már nem a rendszerbuszt terheli a két cache közötti adatforgalom. Ez a megoldás egyrészt csökkenti az adatokhoz való hozzáférés idejét (csökkenti a késleltetést), csökkenti a cache-koherencia szűréséből adódó adatforgalom mértékét (tehát nagyobb sávszélesség marad a hasznos adatok számára), másrészt hatékonyabbá teszi a helykihasználást, hiszen nem kell duplikálni az adatokat ahhoz, hogy mindkét processzormag számára elérhető legyen. A Core processzorok modelltől függően összesen 2 vagy 4 MB L2 cache-en osztoznak, ezt a végrehajtó egységek dinamikusan osztják fel egymás között, tehát erősen többszálú alkalmazások esetében a fentebb vázolt pozitívumokban részesülünk, a gyorsítótár attól függően kerül felosztásra, hogy az egyes végrehajtó egységek milyen gyakran szeretnének hozzáférni a gyorsítótárban található adatokhoz. Ugyanakkor az egyszálon végrehajtott alkalmazások során az egyik processzormag abban a megtiszteltetésben részesülhet, hogy egyedüliként használhatja akár az egész másodszintű gyorsítótárat (ha a másiknak éppen nincs rá szüksége)."

Idézet vége.

A közvetlenül a Core 2 architektúrát követő Nehalem alapú processzorok visszatértek a magonkénti dedikált L2-höz. Jelenleg ezeknél minden mag 256 KB-ból gazdálkodhat, és a jövőre érkező Sandy Bridge esetében is hasonló lesz a helyzet.

IMC Hammer

Az első SledgeHammer kódnevű Athlon64 megjelenése óta (2003 szeptember) a klasszikus értelemben vett Front Side Bus (FSB) mint olyan megszűnt létezni AMD-s vonalon. Ezt megelőzően az FSB főszerepe a processzor és a memóriavezérlőt is tartalmazó alaplapon található északi-híd (North Bridge) összekötése volt. Tehát ha a processzor hozzá akart férni a rendszermemóriához (RAM), akkor ahhoz minden esetben az FSB-->NB-->RAM útvonalat kellett megtennie. Ez egy viszonylag hosszú út volt, aminek eredményeképpen jókora idő veszett kárba, minek okán a késleltetés jelentősen megnőtt.

Az AMD a K8 tervezésénél úgy döntött, hogy az x86-os processzorgyártók között elsőként a gyakorlatban is megvalósítja a CPU-ba integrált memóriavezérlőt (IMC). Így az addigi alaplapok északi-hídjában található memóriavezérlő átkerült a CPU-t tartalmazó szilíciumlapkába, mely ráadásul a mindenkori magórajelen üzemelt. Ezzel egy huszárvágással kiiktatta az FSB-t, aminek következményeképpen a memória hozzáférés sebessége jelentősen javult, és nőtt a valós, mérhetően kihasználható sávszélesség is. Ezzel a K8 generációban elért maximális 3200 MHz a mai napig nehezen felülmúlható alacsony késleltetést tett lehetővé. A mellé költöztetett L3 cache miatt azonban mára vissza kellett fogni az IMC sebességét is. Az FSB helyét a HyperTransport vette át, így azóta AMD-s rendszerek esetében ezen keresztül történik a chipset-tel való kommunikáció, több CPU-t tartalmazó konfigurációk esetében pedig a processzorok közti adatáramlásnak is ez biztosít utat.

A SledgeHammer bevezetésével tehát az AMD végleg leszámolt a külső memóriavezérlőkkel. A fentebb említett dátum óta kizárólag IMC-t tartalmazó lapkákkal szerelt CPU-kat mutatott be a gyártó. Az Intel első IMC-s CPU-ja a Core i7 (Bloomfield) volt mely 2008 novemberében debütált. Az AMD-vel ellentétben az Intel még ma is gyárt off-die memóriavezérlővel szerelt CPU-t. Ezek a Clarkdale/Arrandale lapkákra épülő Core i3 és i5 (mobil vonalon i7 is) processzorok melyek felépítéséről itt lehet egy kicsit bővebben olvasni. Előreláthatólag a Sandy Bridge eljövetelével az Intel is teljesen felhagy a külső vezérlőkkel.

Az évek folyamán egyre több külső egység lelt új otthonra a CPU-k lapkájának berkeiben, mellyel szépen lassan átfogalmazódott ezen hárombetűs rövidítés mögött rejlő szilíciumlapka feladata. Az hogy az idők során pontosan mikor milyen részegységeket foglalt magában a CPU, vagy éppen egyetlen mag, az mindig az éppen aktuális gyártók által diktált trendtől függött és függ ma is. A változás természetesen nem áll meg. Elég csak arra gondolnunk, hogy már egy ideje itt toporog a küszöbön a GPU-k integrációja, de az északi-híd (már ami néhol még maradt belőle) minden szintről való elpárolgása sincs túl messze. Ez gyakorlatilag az Intel Lynnfield kódnevű lapkájával már bő egy éve el is kezdődött mely tartalmaz egy 16 sávos PCI Express vezérlőt.

A következőkben arra is megpróbálunk választ találni, hogy az AMD következő "Bulldozer" néven emlegetett architektúrája mennyiben próbálja átfogalmazni a CPU-k felépítéséről jelenleg alkotott képet.

A cikk még nem ért véget, kérlek, lapozz!