Új gyártástechnológia...

Új gyártástechnológia...

Az első Bulldozer alapú megoldások egy új, az AMD által még valamikor 2007-ben elkezdett, majd a gyártás kiszervezése után a Globalfoundries által tovább vitt fejlesztésű 32nm-es gyártástechnológiára fognak épülni. Ez egyesíti egy az Intel által 45nm-en bevezetett megoldásához hasonló, de itt gate-first megvalósításon alapuló HKMG (High-K Metal Gate - magas k együtthatós fémkapu tranzisztor) technológiát, és az AMD által már az első Athlon 64-ek és Opteron-ok (~2003) óta szinte folyamatosan alkalmazott SOI (Silicon-On-Insulator - szilícium a szigetelőn) technológiáját. Ezen túlmenően a 45nm-es Deneb és Shanghai lapkák gyártásánál először alkalmazott immerziós litográfiát is továbbviszik. Ezek ötvözése számottevően növelheti a tranzisztorsűrűséget és csökkentheti a szivárgási áramot.

Az első Orochi kódnevű Bulldozer alapú lapka, amely a technológiát alkalmazni fogja, 11 fémrétegből épül fel. A méretekről egyelőre annyit lehet biztosan tudni, hogy egyetlen modul az L2 cache-vel együtt 30.9 mm²-es területű lesz, mely így 213 millió tranzisztort foglal magába. Összehasonlítás gyanánt a következő ábrán három hasonlóan 32nm-es csíkszélességen készülő eltérő dizájn méreteit láthatjuk.

a 30.9 mm²-es modul

Az adatok birtokában könnyen kiszámolható, hogy a Sandy Bridge egyetlen magjához viszonyítva durván 68%-kal lesz nagyobb egy modul. Azért nem árt megjegyezni, hogy ez utóbbiban pontosan nyolcszor nagyobb L2 cache lapul az SB 256 KB-os méretű másodszintű gyorsítótárához képest. A K10 architektúrás Deneb/Propus továbbcsiszolt magjait tartalmazó Llano (Fusion) két magja, melyek összesen szintén 2 MB L2 cache-t tartalmaznak, 1.1 mm²-rel foglalnak el nagyobb területet. A képen jól látható az is, hogy a nagy cache önmagában mennyi szilíciumot emészt fel.

forrás: www.chip-architect.com

Egy teljes nyolcmagos lapka 8MB L3 cache mellett az előzetes becslések szerint, körülbelül 1.6 milliárd tranzisztort fog összesűríteni egy alig kevesebb mint 300 mm²-es területen. Az esetleges natív négymagos verzió pedig 4MB L3-mal és kevesebb HT link mellett akár 150 mm²-be is beleférhet majd. A négymagos Deneb/Shanghai 6 MB L3 mellett 258 mm², míg a hatmagos Thuban/Istanbul 346 mm² szilíciumot foglal el. A Sandy Bridge négymagos variánsára 225 mm²-t jósolnak a hozzáértők, igaz ebben már egy viszonylag nagy területet elfoglaló GPU és egy PCI Express vezérlő is helyet kap.

a várható lapka fotója - forrás: www.chip-architect.com

A fenti némileg utómunkázott képre érdemes egy kis figyelmet szentelni. Egyrészt ha az egységek elhelyezkedését nem manipulálták nagyon, akkor marad a K10-nél bevezetetthez hasonló elrendezési forma. Másodsorban az L3 cache négy különálló, egyenként 2 MB-os al-cache szeletből fog összeállni. Egy úgynevezett "column-select aliasing" eljárással növelték a szükséges terület felhasználásának hatékonyságát. Ezen felül csökkentették a szivárgási áramot és javították a kihozatali arányt is. A múltban felmerült Z-RAM alkalmazásáról már teljesen letett a bérgyártó, addig a hasonló előnyöket felvonultató T-RAM alkalmazása egyelőre várat magára. Az L3 cache 2.4GHz feletti alapórajelen fog üzemelni.

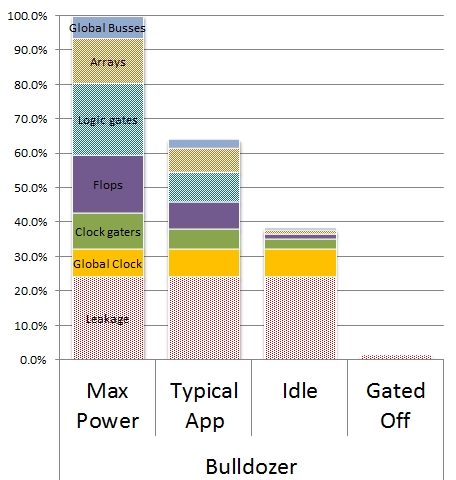

A fogyasztás csökkentésének érdekében is számos újítás kerül bevezetésre a gyártástechnológia és az energiamenedzsment terén. Az órajelkapuzást követően implementálásra kerül a Nehalem-ben már feltűnt tápkapuzás is. A SOI gyártástechnológiának köszönhetően rendelkezésre álló tízszer hatékonyabb, NFET tápkapuzó tranzisztorok használatával a kapcsolóüzemű működésből eredő veszteség mellett a szivárgási áram is a zéró közelébe redukálható az éppen inaktív egységeknél. Így egy adott lekapcsolt rész teljes fogyasztása szinte nullára csökkenhet. Ilyen egység lehet majd például egy teljes modul is.

Mindemellett integrálásra kerül egy külön önálló vezérlő is (a teljes lapka fotóján a "power control module"), ami a K10-ben bevezetésre került rendszer továbbfejlesztése. Ez folyamatosan monitorozni fogja a modulok és a többi főbb részegység aktuális terhelését, áramellátását, fogyasztását és hőmérsékletét. Amelyik egységre éppen nincs szükség és a tervezésből adódóan alkalmas rá, azt a másodperc tört része alatt mély álomba ringatja (C6 - deep sleep), bizonyos, erre felkészített aktív egységek órajelét pedig a szükséghez és lehetőségekhez mérten megemeli (Turbo Core).

A magok működéséhez szükséges feszültség (~CPU Vcore) most sem módosul jelentősen. Az érték az éppen aktív P-STATE-től függően 0.8 és 1.3 volt között dinamikusan változik majd.

A cikk még nem ért véget, kérlek, lapozz!